随着物联网、移动设备和智能终端的爆发式增长,人工智能正加速从云端向边缘和终端迁移。在这一趋势下,传统以计算为中心的冯·诺依曼架构,因数据在处理器与存储器之间频繁移动而产生的“内存墙”和“功耗墙”问题日益凸显。端侧智能存算一体芯片,作为突破这一瓶颈的关键技术路径,正成为学术界与产业界关注的焦点。它旨在将数据处理与存储深度融合,直接在存储器内部或附近完成计算,从而开启高效、低功耗的智能计算新范式。

一、核心需求:为何需要端侧存算一体?

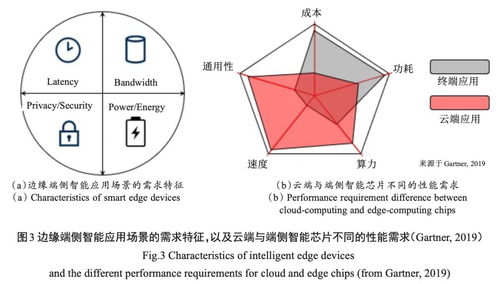

- 实时性与低延迟:自动驾驶、工业质检、AR/VR等应用要求毫秒甚至微秒级的实时响应。传统架构中数据往返于内存与CPU/GPU的延迟无法满足需求,存算一体通过近数据计算极大缩短了数据搬运路径。

- 能效比至上:终端设备受电池续航和散热限制,对功耗极为敏感。数据搬运的能耗远高于计算本身,存算一体能显著减少数据移动,是实现超低功耗AI推理的关键。

- 隐私与安全:在终端本地完成数据处理,避免了敏感数据上传至云端,降低了数据泄露风险,符合日益严格的数据隐私法规要求。

- 带宽压力缓解:高分辨率传感器(如摄像头)产生的海量数据对芯片内部和外部总线带宽构成巨大压力。存算一体通过就地处理,减轻了带宽负担。

二、发展现状:从探索走向初步落地

当前,端侧存算一体芯片的发展呈现多元技术路径并进的局面:

- 技术路线:主要分为数字存算一体(基于SRAM、DRAM等传统存储器,采用数字电路实现乘累加运算)和模拟存算一体(利用非易失性存储器如RRAM、PCM、MRAM的物理特性,如电阻值,直接进行模拟域计算)。前者设计相对成熟,易于集成;后者在能效和密度上潜力巨大,但面临工艺、精度等挑战。

- 研发与产品化:学术界已有大量原型芯片验证,展示了数十到数百倍的能效提升。产业界,如知存科技、九天睿芯等初创公司,以及英特尔、三星等巨头,均已推出或正在研发针对语音识别、图像处理等特定场景的存算一体芯片或IP,部分已进入商用试点阶段。

- 应用聚焦:目前主要瞄准轻量级神经网络推理任务,如关键字检测、图像分类、手势识别等,在智能耳机、手机、摄像头、可穿戴设备中展现应用前景。

三、严峻挑战:通往大规模应用之路

尽管前景广阔,端侧存算一体芯片仍面临一系列核心挑战:

- 精度与可靠性:尤其是模拟存算一体,受器件非理想特性(如涨落、非线性)影响,计算精度难以达到传统数字处理器的水平,制约了其在复杂模型中的应用。

- 工艺与制造成本:新型非易失存储器与标准CMOS工艺的集成难度大,良率控制和制造成本高昂,是产业化的主要障碍。

- 设计工具与生态缺失:完全缺乏像传统EDA那样的成熟设计工具链、编译器、编程模型和软件生态,开发门槛极高。

- 灵活性不足:现有存算一体架构多为特定算法(如CNN)优化,通用性和可编程性较弱,难以适应快速演进的AI算法。

- 测试与验证难题:尤其是模拟计算,其测试方法和标准尚未建立,验证复杂度高。

四、数据处理与存储的范式变革

存算一体芯片的核心在于对数据处理与存储关系的重构:

- 从“存储-搬运-计算”到“在存储中计算”:计算单元深度嵌入存储阵列(如内存单元本身成为计算基元),或与存储单元紧耦合,实现了真正的“数据不动计算动”或“计算不动数据动”。

- 数据流重构:计算以数据为中心进行组织,特别适合神经网络中大量的乘累加并行运算,实现了极高的计算并行度和数据复用率。

- 存储介质即算力:不同的存储技术(如RRAM的高密度、低功耗,SRAM的高速度)决定了不同的计算特性和适用场景,存储器的选择成为芯片架构定义的核心。

- 层次化智能存储:未来可能出现在芯片内集成不同特性的存算一体模块,形成层次化处理结构,智能地分配和调度任务,实现能效与性能的最优平衡。

端侧智能存算一体芯片是应对后摩尔时代计算能效危机的革命性探索。它深刻契合了边缘智能对实时、低功耗、高隐私的刚性需求。虽然目前仍在精度、生态、成本等挑战中攻坚,但其在特定场景的成功应用已证明了技术路线的可行性。随着材料、器件、架构和工具链的持续突破,存算一体有望从专用加速器向更通用的智能计算平台演进,最终成为赋能万物智能感知与决策的底层基石,推动人工智能在终端侧的无缝融合与普惠发展。